Вы видите копию треда, сохраненную 31 мая 2021 года.

Можете попробовать обновить страницу, чтобы увидеть актуальную версию.

Скачать тред: только с превью, с превью и прикрепленными файлами.

Второй вариант может долго скачиваться. Файлы будут только в живых или недавно утонувших тредах. Подробнее

Если вам полезен архив М.Двача, пожертвуйте на оплату сервера.

77 Кб, 500x920

77 Кб, 500x920>ап

Ты не сильно умный, как я погляжу. Ту ли ты профессию выбрал? Может дворником тебе более комфортно будет?

https://2ch.hk/ra/res/127314.html (

Ебани логический анализатор каналов на восемь с парой мегабайт записи, распознаванием паттернов и совместимостью с распространенными программами анализа. Можно, чтобы еще и светодиодом моргал.

учи лучше джаву. На плисах будешь залупу последнюю без соли доедать

нихуя ты долбаёб братишка, земля тебе пухом.

ВО первых - джава для петухов.

Во вторых - мне похуй на зарплату ибо я уже положил крест на свою жизнь и в дальнейшем буду преподом дискретной математики.

В третьих - плис это ахуенно интересно и если твоих пропитанных джавапарашей мозгов не хватает чтобы понять как оно и зачем - это не значит что направление тлен

>плис это ахуенно интересно и если твоих пропитанных джавапарашей мозгов не хватает чтобы понять как оно и зачем - это не значит что направление тлен

Если бы ты понимал как оно и зачем то не задавал бы здесь тупых вопросов. Про то, что продублировал тред и бампаешь в тематике я вообще молчу. Залетное озлобленное говно из /b видно с порога.

>мне похуй на зарплату ибо я уже положил крест на свою жизнь

Похуй на зп, пока твой мозг пропитан говном и юношеским максимализмом, со временем это пройдет, но чтоб не было поздно я дал тебе бесплатный совет - просто сравни количество вакансий и вилку зп на hh.ru по fpga и java и все поймешь.

Тот тред уже достиг бамплимита и медленно тонет. Надо либо новый оффициальный™ тред делать, либо сюда перекатываться и бортануть ОПа, раз уж создали.

>либо сюда перекатываться

Давай перекатываться. Задам свой вопрос тут.

ПЛИСаны, я не понял, вот я насинтезировал конфигурацию и залил ее в эту вашу FPGA, отключил питание и все пропало? Это мне надо отдельный контроллер мутить, чтобы каждый раз конфигураци. закидывать в нее?

Обычно ставят специальное ПЗУ, иногда загружают из микроконтроллера. Если у тебя отладочная плата, то там должно быть ПЗУ.

Почти. Потребуется отдельное, специально обученное ПЗУ с SPI интерфейсом:

https://www.eevblog.com/forum/microcontrollers/cyclone-v-configuration-using-spi/

>Если у тебя отладочная плата,

Нет, хочу мутить частотомер, а тут начитался про то что FPGA_NOT_CPLD

> А как быть с четвертым Циклоном?

Ты это, по ссылке то ходить пробовал?

> I have used Winbond and ST flashes in the past for Cyclone IV and Spartan III without any issues.

Хорошо, что ты не моряк.

Ставишь какую-нибудь EPCS и все. И вообще для обыкновенного частотомера не нужны FPGA и вообще ПЛИС, из-за низких частот в том числе.

>>17915

Так и в пятых циклонах нет микроконтроллера, там просто ядро. В FPGA (обычно) нет флеша потому что технологии изготовления FPGA и флеша чем-то отличаются.

У некоторых есть, но это отдельный продукт и за отдельные деньги: https://www.altera.com/products/soc/portfolio/cyclone-v-soc/overview.html

Какой же это микроконтроллер без флеша? Хотя, кому-как, наверное, ведь нет четкого определения того что считать микроконтроллером.

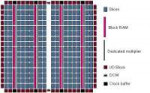

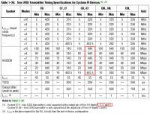

![Screenshot-2018-3-29 Cyclone IV Device Handbook - cyclone4-[...].png](/ra/big/thumb/316943/15223481552240s.jpg) 48 Кб, 745x470

48 Кб, 745x470Достаточно EPCS4. Также у этих ПЗУ есть полностью совместимые аналоги.

На всякий случай еще раз скажу: нет смысла использовать FPGA для простого частотомера. На FPGA не получится сделать быстрый счетчик. Целесообразнее использовать быстрый счетчик и любой микроконтроллер.

>На FPGA не получится сделать быстрый счетчик

Да ладно? Что он 200МГц не потянет? Мне больше и не надо.

Потянет, но 74VHC4040 с любым микроконтроллером также потянет.

Почему сразу не сказал? Вроде как банальная память 25 серии может быть аналогом, и местами даже более быстрым, и добываемым из ближайшей помойки.

Как-то долбил ЭФО на тему оригинальных EPCS - это ахтунг, если сравнивать с "обычной" 25 серией:

EPCS4SI8N 4,5$/шт, DC 15+ Есть на складе СПб, доставка 1-1,5 недель

EPCS16SI8N 6,6$/шт, DC 16+ Есть на складе СПб, доставка 1-1,5 недель

25-ю серию сам еще не запускал, только в каком-то AN читал и на electronix.ru (https://electronix.ru/forum/lofiversion/index.php/t57150.html).

ЗЫ - Какие сейчас есть не сильно древние FPGA с 5В входом и выходом ?

Еще раз - ВХОДОМ и ВЫХОДОМ, а НЕ 5V-tolerant input. Честные 5В входы-выходы и было бы очень неплохо чтобы и другие напряжения держало (3.3, 2.5)..

Altera FLEX, ACEX и прочие ? С софтом проблемы. Или плохо смотрел? Есть CLPD на 44 вывода LC4064V - у нее 2 банка VCCIO - в теории по даташиту можно осторожно подать 3.3 и 5В.

> не сильно древние FPGA с 5В входом и выходом

Выбери одно Пятивольтовые FPGA померли лет 20 назад, CPLD продержались дольше, но что MAX7000S, что XC9500 давно сняты с производства.

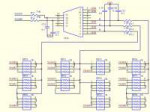

1,4 Мб, 3264x2448

1,4 Мб, 3264x2448Кто-то в теме? Уже прилично так посношал гугл, а он так и не дает ответа, как и 9-й кактус - у Flex 10K%30RI208-4% есть разделение пользовательских выводов по банкам напряжений питания или нет? На сайте альтеры в разделе pinouts какие-то мутные документы, где описаны только служебные выводы, а про обычные(пользовательские) ни слова.

Видимо остановлюсь пока что на Flex 10K.

MAX7000S - тоже есть для ловли баттхерта от заявленных максимум 100 перепрошивок.

У EPM7128SLC84 - точно нет разделения выводов на банки - или все 3.3 или все 5В..

>от заявленных максимум 100 перепрошивок.

Народ пишет, что тысячи раз шили и нихуя страшного не случилось. Это типа Альтера перестраховуется, чтобы в случае чего ей мозги не ебли.

Ты делаешь что-то странное, если тебе понадобились 5В уровни и при этом не подходит преобразователь уровней. Также оно стоит немало, если покупать с хоть какой-то гарантией.

>есть разделение пользовательских выводов по банкам напряжений питания или нет?

https://www.altera.com/en_US/pdfs/literature/an/an107.pdf Банков там нет. 5В одновременно с 3,3В на выходах (вроде бы) обеспечиватеся за счет внешнего подтягивающего резистора.

>100 перепрошивок

Эти 100 перепрошивок - это количество перепрошивок при котором гарантируется заданное время сохранности данных во флеше. Если превысить, то производитель (всего лишь) не гарантирует что конфигурация будет сохраняться заданное время.

Народ, а в даркнете еще не пробегала схема chipprog 48 с конфигурацией FPGA?

2,6 Мб, 3258x2168

2,6 Мб, 3258x2168Теплые, ламповые 5В.. Один раз был случай когда надо было немного логики в разрыв впихнуть, а не из чего, а свеженький циклон стремно было пихать, как и нормальные преобразователи 8T245 (или подобные) с 2 напряжениями питания негде было выдрать.

>Ты делаешь что-то странное

Тяжелый осадок одной истории.

Еще раз перечитал - по ходу да, банков нет. Подав 5В на все VCCIO и получаем 5В ввод-вывод. Согласование выходов вниз (до 3.3) на резисторах, входов не нужно.

Про 100 перепрошивок - читал на марсоходе как они издевались, но там была cpld намного свежее в виде epm240, а не архаичной max7000.

FPGA хороша тем, что у нее нет ресурса перепрошивок, но и отладка как на МК - это порочная практика. Синтез проекта, заливка, оценка работы в реальном железе, правка, повторная заливка..

MAX10 показалась интересной - заливая через JTAG конфигурацию - она применяется. Передернув по питанию - грузится "заводская" конфигурация. Как минимум ресурс внутреннего флеша не должен уменьшаться.

Есть на чем проверять, а мозгов для укрощения пока нет. Пробую VHDL неспешно изучать.

Антон выручай.

Altera Flex 10K поймет новую память 25 серии (какую-то некрофилию на мегабит-другой(из которых всего 46 килобайт используется) через преобразователь уровней) для хранения и загрузки конфигурации?

По диагонали почитал AN116 - вроде возможно же. Как и поймет ли прямую запись pof файла или же преобразованного hex в конфигурационную flash?

Это про 4-ый циклон, а тот анон про флексы.

>>18805

Стоит посмотреть http://db.zmitac.aei.polsl.pl/Electronics_Firm_Docs/ATMEL/Atmel/acrobat/doc0910.pdf

Забавный костыль. Закопипастил страничку - вдруг пригодится.

>>18822

Уже читал эту статейку и про их согласование уровней на hc244. http://www.platan.ru/shem/pdf/st50-52.pdf

Даташиты не сравнивал.

Это было сложно нагуглить по памяти:

https://electronix.ru/forum/lofiversion/index.php/t13569.html

как наебать систему и не подать виду.

Даже если будет эпикфейл - фигня.

Тут тоже нет конфигурационной памяти у флекса (хотя и есть куда ее втыкать) https://habrahabr.ru/post/277947/

Этот антон прав. Почитал даташиты - никаких шансов приклеить 25 серию флеша к флексу. Заглянув в efind.ru и chipfind.ru в поисках epc1 epc2 at17 - прямо как на той картинке "все ебанулись". Стоят как крыло от самолета.

И ладно.. Главное питание на рабочей схеме не дергать. На Altera UP1 (UP2) было только куда ставить саму память, но памяти не было. Вариант с МК конфигурить не рассматривал, хотя он скорее всего будет основным.

Этот артефакт даже подает признаки жизни.

Входы и выходы прибиты гвоздями на 5В. Пока что все.

Парни, хелп. Нужная плата для акселерации вычислений. Суть в том, что она цепляется по эзернету, получает задания-считает-возвращает результат. Я нихрена не знаю, наугад предложил взять AES-KU040-DB-G

http://ru.farnell.com/avnet/aes-ku040-db-g/dev-board-kintex-ultrascale-prog/dp/2775206?st=kintex

Может есть что-то с более оптимальным соотношением цена/производительность?

И если заказывать с фарнелл - не завернёт ли таможня? Пугают буквы "AES" в названии.

Нужно исходить из ресурсозатрат твоего алгоритма.

>Пугают буквы "AES" в названии.

Иностранные поставщики соблюдают законодательство РФ горазбо более скурпулезней, чем пидорахен-таможня. Если согласятся отправить 90% что таможня пропустит.

Алсо в рашку могут поставляться платы с выжженными блоками AES

Ты бы хоть в документации поискал прежде чем ерунду писать. В последнем поколении альтеровских FPGA имеется AES для шифрования конфигурации.

Бля, я не говорю что AES там нет, я говорю что AES в названии не о шифровании.

Блоки для крипты прошивки они клепают уже давно, и всем похуй.... экспортируються даже в санкционную рашку

Можешь хоть что-нибудь предоставить в доказательство? Я покупал в терраэлектронике микроконтроллеры с аппаратным AES и они пришли в фарнеловской упаковке, все вроде как работает.

И потом, как вообще можно выжечь какой-то блок, причем не задев соседние, если это не было предусмотрено при проектировании микросхемы?

Кроме того уже прошел месяц, наверное для анона задававшего вопрос это уже не актуально.

>И потом, как вообще можно выжечь какой-то блок, причем не задев соседние, если это не было предусмотрено при проектировании микросхемы?

ФЬЮ

@

ЗЫ

Дык на них есть нотификации фсб, а есть ли они на платы с плис - большой вопрос. В треде про компутеруниверс на /hw много разговоров про это. Есть две видюхи, аналогичные по характеристикам, одну можно невозбранно купить, а за другую чуть ли не присесть за ввоз антироссийского шифрующего средства. Как-то так, правда я слышал что эту шнягу потом отменили но это не точно.

Хочу прикупить тут чип XC7K355T-2FFG901I для своего девайса, смотрю цены, на фарнелл оно стоит €1 819,00. На ебее и на али встречаются цены от 12т.р. (€163,79) за чип. Это что наёбка какая-то? Откуда такой разброс цен?

https://www.ebay.com/itm/2PCS-X-XC7K355T-1FFG901C-IC-FPGA-300-I-O-901FCBGA-Xilinx/332337611117?epid=2165454311&hash=item4d60dd816d:g:MZwAAOSwPfVZi2I0

http://ru.farnell.com/xilinx/xc7k355t-2ffg901i/fpga-kintex-7-300-i-o-fcbga-901/dp/2831130?st=XC7K355T

и разный speed grade

F: XC7K355T-1FFG901C

E: XC7K355T-2FFG901I

-1 -2 - скорость

С I -температурный

Нет ничего больней перекатывания с няшного верилога на вхдл.

Ну если только переход с квартуса на вивадо. Хотя там симуляция проще.

Хоспаде, за что тебе такое??!

Тем не менее, всяких багуль, решающихся закрытием проекта, я тут словил уже больше.

>Просто петушиное бинго сорвал.

Ну и дрочи дальше свои

иклюд дибрари ИЕЕЕ_СТД_ВЕКТОРА_МАТИМАТИКА

сигнал стд_лоджик_вектор(10 даун ту 0)

when => <=

Что это вообще блять такое тут присходит. Ебануться.

Багули ты ловишь, потому что руки из жопы растут. А что касается дрочи дальше, так это не я вынужден перейти на вхдл, а ты. Так что да, дрочи дальше.

Начни с подачи постоянного напряжения на вход АЦП. В твоем случае - от 1 до 3В. Подал напряжение, записал отсчеты, посмотрел че получилось, поменял напряжение. Поставь себе какой-нибудь Bitviewer, чтобы было проще смотреть че у тебя записывается в файл.

И да, у тебя отлажена схема записи в память/чтения из памяти/передачи по UART?

>Bitviewer

Чем оно лучше калькулятора в виндовсе?

>И да, у тебя отлажена схема записи в память/чтения из памяти/передачи по UART?

Было бы что там отлаживать, простейшая же ерунда. Я тоже делал такое, только в отличие от этого анона я писал по 32 бита и принимал в матлабе.

>>3244592

Похоже последовательность байт перепутана.

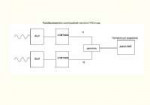

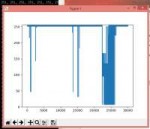

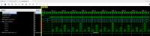

384 Кб, 1200x644

384 Кб, 1200x644>Чем оно лучше калькулятора в виндовсе?

Калькулятор может нарисовать что-то такое?

>Было бы что там отлаживать, простейшая же ерунда. Я тоже делал такое, только в отличие от этого анона я писал по 32 бита и принимал в матлабе.

Молодец. Но я спрашивал не у тебя, а у этого анона.

Может неактуально, но...

Сделай мультикатридж для для денди на микроконтроллере, а плис будет выполнять роль маппера.

Ну выучи и поднимай. Хотя мне кажется, что там тоже много знать надо, чтобы хорошо платили.

Это не навыки. Я про алгоритмы, хуе мое.

То, что нужно сидеть в виваде под сисверилгом\вхдл плисоебу - это очевидно.

Си, я так понимаю, уже для скриптом в микроблейзе\цинке?

Это в оборонке такое хотят? С одной стороны, не представляю, кто в рашке может платить за плисоёбство, кроме оборонки, с другой, систем верилог и пайтон — для оборонки очень по-хипстерски.

В оборонке хотят железо. Как ты это железо будешь кодить никого не волнует.

Ну, из алгоритмов это фильтрация, ресэмплинг сигналов, различные виды модуляции, прием сигналов спутниковой связи, ФАПЧ, временные синхронизации, тактовые синхронизации, АРУ, Витерби, BCJR, LDPC и т.д. и т.п.

На C/C++ пишешь модели разрабатываемых алгоритмов, а потом переносишь на ПЛИС, или чужие модели, написанные на C/C++ переносишь на ПЛИС.

кек

Я третий в этом тредю и мы, кажется, все в одном отделе сидим, лул.

3 форма допуска, похуй.

Антихайп, ебал твой рот.

Я вот о чем.

Был у меня msg STD_LOGIC_VECTOR, в котором вручную забито сообщение в хексе в аскии.

И которое я спокойно пересылал с помощью мультиплексора, мол, если первый бит, то отсылаю из этого вектора кусок от 7 до 0. case i when b"00" => data(7 downto 0) <= msg(7 downto 0) и т.д.

Но надо быть человеком и использовать массивы, тайпы, хуяйпы. Как мне объявить мое сообщение? Как мне обращаться к его кускам по индексу, если у меня индекс-счетчик изначально тоже вектор?

Если забиваю на вектор-счетчик и делаю отдельный integer для индекса, то всё равно при обращении к массиву типа msg(7 downto 0) пишет, мол, внутри msg нихуя не вектор и иди нахуй. Колбасная магия с приведением типов to_unteger(unsigned i) это тоже отдельная песня.

Фокус с циклическим сдвигом ror тоже, кстати, не работает. Мол, не определена операция и всё такое.

Итак, еще раз. Как передавать символы по одному используя в качестве исходных данных массив? И всё должно быть, естественно, синтезируемо.

Спасибо.

Что-то не вполне тебя понял. Я VHDL подзабыл, но все равно как-то написал пример.

Если этот "массив" довольно большой, то целесообразно использовать блочную память. В таком случае имеет смысл организовать код таким образом, чтобы можно было заменить память на примитивы и мегафункции всякие, если вдруг синтезируется не так. К тому же так меньше вероятность сделать ошибку и получить какую-нибудь трехпортовую память.

Ну вот у меня есть Hello.

Я его объявлял

constant msg : std_logic_vector(39 downto 0) := X"68656c6c6f"

И обращался

case cnt is

when B"00" => data <= msg(7 downto 0) ...

Вот захотел не писать этот ебаный мультиплексор с кейсами, а как белый человек, через переменную. Но переменная у меня лоджик вектор, которую так просто не засунешь в скобки, нужно приводить в to_integer(unsigned()).

Как вообще на синтезируемость влияют эти все конвертации, какая предсказуемость результата?

Далее. Не хочу задавать явно в хексе вручную. Хочу писать

constant msg : string := "Hello"

И чтобы достать конкретную букву, соответственно писать

if rising_edge(clk) and (cnt <8) then

data(7 downto 0) = msg(cnt)

Но тут уже ругается, что msg(cnt) выдаёт не биты, в которых блять тут все должно хранится,, а, собсно, букву. Опять нашел, что стринг это массив чаров, которые тоже можно там по ебаному как-то конверсить в нормальные биты.

>Но переменная у меня лоджик вектор, которую так просто не засунешь в скобки, нужно приводить в to_integer(unsigned()).

Приводи, в чем проблема? Тут же строгая типизация.

>мультиплексор

В данном случае это скорее дешифратор.

>Как вообще на синтезируемость влияют эти все конвертации, какая предсказуемость результата?

Лучше посмотри исходники ieee.std_logic_1164, которые должны быть в твоем САПР и симуляторе. Там будет видно, что unsigned и std_logic_vector отличаются только тем, что для них определены разные операторы/функции. А определения этих обоих типов абсолютно одинаковые.

>это массив чаров

Которые имеют перечислимый тип. И прописаны они в пакете STANDARD, исходники которого также везде имеются.

>Приводи, в чем проблема?

Для меня это всё еще выглядит черным ящиком и магией коньпилятора, когда не ясно, что там внутри на уровне схематики происходит.

Хотя вот раз говорят, что это всё ходы, чтобы обмануть сапр, а на самом деле там внутри одно и то же байтоебство, то буду менее настороженно к этому относиться. Но выглядит всё равно некрасивенько.

>В данном случае это скорее дешифратор.

Верно, извиняюсь.

С индексом разобрались, вектор в ансайнд, оттуда в интежер.

А что с обращением к символу в строке, как его в биты перевести?

Свою функцию перевода писать, как рекомендуют?

function to_slv(c: character) return std_logic_vector is

begin

return std_logic_vector(to_unsigned(character'pos(c)), 8));

end;

А еще пишут, что стринг не синтезируема. Значит мне строки в каком формате объявлять?

Тогда используй string только при инициализации std_logic_vector. Аналогично тому, как инициализируют RAM из файла.

Слишком уже задротская тема какая-то. Я начинал с нубовопроса, не знаю уже, о чем речь.

Можно на огромной скорости молотить в логике операции, которые процессорное ядро на такой скорости не вытянет. А ядро будет заниматься всем остальным. Бесценно для обработки сигналов.

Просто без задней мысли пишешь на верилоге и не забиваешь голову всякими АЙЕЕЕ_СТД_ЛОДИК_ВЕКТОР

Да, я тоже любил великолепный верилог, но увы, не разрешают.

>Бесценно для обработки сигналов.

В ПЛИС есть встроенный ацп или предполагается использовать дорогой внешний? И цап тоже внешний?

Ну сигналы есть не только аналоговые. Обработку эзернета, например, можно замутить.

Нахер оно нужно? Лучше уж готовый копеечный езернет контроллер поставить.

Вот высокоточная обработка и анализ СВЧ аналога в реалтайме - интересная тема. Но нужны оче дорогие ацп и цап.

Куда копать для вкатывания в тему и освоения DSP?

Разве? В одном из самых простеньких циклонов EP4CE22 (который я люблю за TQFP корпус), есть 66 умножителей 18х18 бит, которые могут работать на ~200МГц. Параллельно умножителям там может работать куча сумматоров. Безусловно, какие-то DSP такое потянут, но если взять ПЛИС побольше?

49 Кб, 1076x846

49 Кб, 1076x846А если критична задержка и надо фильтровать пакеты на 7-м уровне osi на скорости 10 гигабит? А если надо выполнять ещё расчёты и выдавать отклик? На плис такая задержка будет минимальной, можно выстроить схему так, что расчёт будет идти конвеером и сложный алгоритм будет выполнятся за пару тактов, на проце такое сделать иногда просто невозможно, или нужна многоядерная йоба и ртос, и это будет нихуя не дешевле плис и разработка намного сложнее будет.

>>25715

Есть такое.

>это всё ходы, чтобы обмануть сапр

Именно. По сути преобразование типов - это преобразование метаинформации о битах, а не самих битов.

>>25625

>Слишком уже задротская тема какая-то

Когда я еще наивно полагал, что vhdl это неплохой язык, наткнулся на https://github.com/VLSI-EDA/PoC библиотеку, которая немного упростила байтоебство. Ничего лучше под этот язык пока не знаю.

>4 GSPS 12-bit RF-ADC

>Есть такое

>В плис

Разве что где-то в лаборотории у хилых. В рельности доступны только 1 MSPS.

53 Кб, 326x500

53 Кб, 326x500Прошу вашей консультации. Дело таково.

Мне нужно знать, можно ли сэкономить транзисторный бюджет и скорость, заменив стандартный float16 вычислитель на некую имитацию с фиксированной точкой.

Что мне нужно. Допустим умножать.

Каковы особенности чисел?

1. Со знаком.

2. Фиксированная точка (на десятых долях допустим) 2.1 1.3 4356.5

3. Но, когда число в диапазоне (-1 1), точку нужно перенести в старший разряд, для макс точности. Например 0.124321 -0.932323

А результат пишется в большой регистр в формате с фиксированной точкой. Например 435626.124321

941 Кб, 1280x960

941 Кб, 1280x960В более старых платах у них второй спартан стоит, ничего нового.

Годная пикча.

Современные погромисты даже не знают как устроена мышь и контроллер дисплея, а про архитектуру процессора я вообще молчу

Радачеры как макаки же. Кнопочки даваить и паять научились, а как все устроено подробно не знают и знать не хотят в большинстве

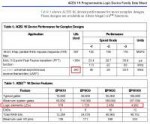

18 Кб, 740x216

18 Кб, 740x216>Современные погромисты

Ты из какого НИИ им. тов. Подзалупкина вылез? Кому впёрлись твои расчёты когда у нас аппликашка календарика на мобиле загружает под 100% 4 ядра по 1.4Ггц просто красивенькими анимациями и полупрозрачными 3д переходами? Здесь другие ребята, анон, не стоит шутить про расчёты, это тебе не шиндоус 3.1, здесь абстрагируются по-крупному. Здесь пишут на языке богов, где любая сущность объект, где всё наследуется от всего, где просто хэллоуворлд может занимать тысячи строк кода и при внесении пары изменений в коде управлять заодно ядерным распадом в коллайдере, здесь шаблон погоняет кодогенерацией, здесь просто приложение с показом времени отжирает 2 гига оперативы на старте и занимает 500 мегабайт на диске. Тут используют Анриал Енджин только чтобы перемножать пару матриц в его математической библиотеке, здесь гарбадж коллектор трахают прямо в анус, создавая тысячи объектов в каждом кадре и не освобождая ручками ни один.

Забудь ты про свой найтивный код. Здесь совсем другая тема. Тут программируют совсем на другом уровне.

Хуясе! Как это у меня паста автоматом конвертнулась в пнг и запостилась пикчей? Это Абу там устои расшатывает?

Ну короче не те уже вы

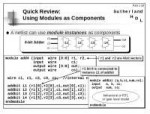

115 Кб, 658x2541

115 Кб, 658x2541>На каком принципе работает курсор? Как определяют координаты и взаимодействие к примеру с окном?

>А где можно подробнее глянуть про контррллер дисплей? Как он формирует текст?

Это опять ты вылез?

Это не радачеры тупые, а ты. Не можешь даже оответствующую литературу прочитать. Как вообще тебе объяснять, если ты не знаешь базовых вещей?

Вот на картинке мой код простейшего процессора, много ты понял? А если нарисовать это на отдельных регистрах и счетчиках? Нихуя ты не поймешь, потому что "регистр" — для тебя пустой звук.

Ну, можешь попытаться все это понять с помощью nand2tetris — это такой курс для тупых программистов. Но ты сейчас опять в лучшем случае поблагодаришь и продолжишь писать тупняк.

А картинка выглядит просто шуткой. Любой человек, пишущий на ассемблере, сможет вручную по таблице опкодов перевести текст в машинные коды. Остальная "иерархия" также имеет мало смысла.

И как твой код переводится в машинный? Где эта прога нахожится, что переводит?

Ну про курср правда интересно. Про регистры я читал

>И как твой код переводится в машинный? Где эта прога нахожится, что переводит?

Оказывается ты тупее, чем мне казалось раньше. Заголовок треда не видел?

Поскольку ты такой тупой, все же попытаюсь объяснить. Этот код, в некотором приближении, можно считать схемой в текстовом виде. Специальная программа (в первом приближении) располагает эту схему внутри ПЛИС так, чтобы она занимала меньше места. Так же как в случае с ассемблером, любой плисоеб, может вручную, без компа перевести этот код в схему (но не внутри ПЛИС, по разным причинам).

>Про регистры я читал

Но нихуя не понял, иначе не писал бы тут тупняк.

Ты из какого НИИ им. тов. Подзалупкина вылез? Кому впёрлись твои расчёты когда у нас аппликашка календарика на мобиле загружает под 100% 4 ядра по 1.4Ггц просто красивенькими анимациями и полупрозрачными 3д переходами? Здесь другие ребята, анон, не стоит шутить про расчёты, это тебе не шиндоус 3.1, здесь абстрагируются по-крупному. Здесь пишут на языке богов, где любая сущность объект, где всё наследуется от всего, где просто хэллоуворлд может занимать тысячи строк кода и при внесении пары изменений в коде управлять заодно ядерным распадом в коллайдере, здесь шаблон погоняет кодогенерацией, здесь просто приложение с показом времени отжирает 2 гига оперативы на старте и занимает 500 мегабайт на диске. Тут используют Анриал Енджин только чтобы перемножать пару матриц в его математической библиотеке, здесь гарбадж коллектор трахают прямо в анус, создавая тысячи объектов в каждом кадре и не освобождая ручками ни один.

Забудь ты про свой найтивный код. Здесь совсем другая тема. Тут программируют совсем на другом уровне.

Лол. Спасибо за терпение. Я про плис не спрашивал т.к. не разбирался с ним и не собираюсь пока.

Я просто тут часто спрашивал и всех заебал про ассемблер. Я так понял, что сам кодер опкодов в машинный заложен уже в архитектуре проца. Но сам ассемблер это сорт компилятора?

А про курсор я еще не понял детально. Хочу найти подробные схемы видеоконтроллера кр580вг75

>Я так понял, что сам кодер опкодов в машинный заложен уже в архитектуре проца. Но сам ассемблер это сорт компилятора?

Не, это просто бессмысленный набор слов. Нихуя ты не понял. Абсолютный нуль знаний. Хотя это даже не нуль, ты в минус пошел.

>Хочу найти подробные схемы видеоконтроллера кр580вг75

Опять ты со своим выводом изображения на экран? Ладно, в очередной раз попробую объяснить.

Начинать нужно с аналогового видеосигнала, того который в телевизоре или мониторе на ЭЛТ. В телевизоре электронный луч двигается зигзагом за счет отклоняющего магнитного или электрического поля. Попадая в экран, электроны засвечивают люминофор. Чем больше электронов - тем сильнее свечение. Таким образом, для того чтобы сформировать изображение, нужно менять силу тока электронного луча в кинескопе. Воздействие, заставляющее меняться силу тока, представляет собой видеосигнал (в некотором приближении, т.к. надо еще синхронизировать перемещение луча).

Аналоговый видеосигнал, как и любой аналоговый сигнал, это просто напряжение или другая величина, изменяющаяся во времени. Все, теперь задача процессора с "видеоконтроллером" сводится к формированию заданного аналогового сигнала. А для этого, в самом простом случае, достаточно лишь приделать параллельный ЦАП к параллельному порту и написать программу, которая будет в этот порт выводить требуемые значения. При такой постановке задачи это ничем не отличается от вывода любого другого аналогового сигнала, например звука.

КР580ВГ75 в некотором приближении всего лишь перекладывает часть этой работы с процессора на себя.

Вот в каком месте тебе не понятно? Это даже многие ардуинщики понимают. Те самые, про которых ты так отзывался >>26140

>>26226

Небольшое уточнение. Третье состояние могут проверять оба оператора, но только при симуляции. Это не синтезируется, разумеется. casex помимо "Z" может проверять на "X", вот и все отличие. А для синтеза используется значение "?" (пропускает любое значение).

>набор слов

Ну хорошо, а где тогда находится тот декодер, который код с экрана переводит в машинный? Ты же сам понимаешь, что буквы с экрана не с помощью магии в машинный код переводится.

Да я понимаю, что экран это по сути сетка пикселей, в зависимости от сигнала кода контроллер зажигает определенные пиксели и таким образом формируется изображение.

А как вот курсор работает, обратная связь?

Ты какую-то хуйню городишь. Напиши нормально что ты хочешь узнать. Написаный текст на языке погромироаания переводится в инструкции процессора компилятором. А хуйню с курсором и обратной связью лучше бы не писал

Ты какой-то совсем больной на голову.

>Ну хорошо, а где тогда находится тот декодер, который код с экрана переводит в машинный?

Переводом текста программ в машинный код занимается компилятор. Комилятор это программа такая, если что. Зачем делать компилятор, который будет брать текст с экрана? Не кажется ли тебе логичнее брать текст из файла или какой-нибудь области ОЗУ?

>Ты же сам понимаешь

Нет, твое чириканье я не понимаю. Отдельные слова вроде понятны, но предложения бессмысленные.

>А как вот курсор работает, обратная связь?

Лучше выпились.

Все объяснения как оно работает есть в книгах, которые тебе уже советовали. Причем это книги не для специалистов, а просто для общего развития, понятные не профессионалам. Ты, может быть скажешь, что "читал", но я тебе не верю или ты читал жопой. Попробуй напрягать голову в процессе чтения и отвечать на контрольные вопросы в конце каждой главы.

>Лучше выпились.

Слушай, этот тип, с периодичностью 2-3 месяца, врывается в радач и начинает задавать одни и те же вопросы по кругу. Постоянно находятся сердобольные аноны пытающиеся ему пояснить, хотя все это расписано и разжевано в сотне книг рассчитанных на широкий круг icq. Но этот унылый траль продолжает и продолжает уныло тралить.

Какие книги, посоветуй авторов? Я проебал ссылки

>>26260

>курсор

Ну если ты не знаешь, то так бы и сказал сразу. Если ты не можешь объяснить ребенку на пальцах что то в течении минуты - значит ты это сам не понимаешь

>>26261

Бля. Я не говорю про текст с экрана. Это всего лишь интерфейс для человека поняинтно. Про компилятор знаю, но принцип ты его понимаешь? Ты же вот мне про регистры говорил. Говришь программа переводит, это и так любому школьнику понятно. Ну ты же сам понимаешь, что программа это не магия, а по сути управление логическими элементами и кодерами, которые из этих вентелей и состоят. Так я всего лишь это хотел и узнать - где эти кодеры и находятся - в архитектуре проца или нет. За терпения спасибо тебе конечно. Вы конечно радачеры молодцы, можете делать/собирать йоба устройства и погроммировать, но на уровне микро видимо мало кто понимает, кроме инженеров интела и т.п.

И что я такого задал про курсор плохого? Мне просто интересно, какой принцип.

>Так я всего лишь это хотел и узнать - где эти кодеры и находятся - в архитектуре проца или нет.

У меня аж голова заболела. Кодеры - они за компом, вне проца находятся.

>но на уровне микро

Тебе интересно понять, как проходит движение основных носителей заряда в приповерхностном слое?

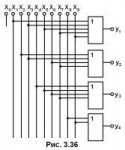

53 Кб, 485x578

53 Кб, 485x578Ну вот тебе элементарный шифратор 10 чисел в двоичные к примеру

Они же находятся уже в архитектуре проца? Я собственно и пытаюсь это у вас тут узнать какой уже месяц лол

Блядь, ебаный ты шизоид, ты можешь нормально выражать свои мысли? Твой поток сознания читать просто не возможно. Возникает ощущение, что у тебя разорванное мышление или речевая бессвязность. Просто словесный шум какой-то. Прими таблетки и не забывай посещать психиатра, у которого наблюдаешься.

>а где тогда находится тот декодер, который код с экрана переводит в машинный

Переводом исходного кода в машинный код занимается компилятор, а не декодер.

>А как вот курсор работает, обратная связь?

По-разному, в зависимости от архитектуры и вида курсора.

>Ну ты же сам понимаешь, что программа это не магия, а по сути управление логическими элементами и кодерами, которые из этих вентелей и состоят.

Программа - это последовательность инструкций процессора. Это по сути. Она управляет вычислениями, а не логическими элементами.

>но на уровне микро видимо мало кто понимает

Нет такого уровня, ты словоблудишь. На уровне цифровой схемотехники понимает любой плисовод, например.

>Если ты не можешь объяснить ребенку на пальцах что то в течении минуты - значит ты это сам не понимаешь.

Глупости. Нельзя научить, можно только научиться. Раз ты называешь дураком того, кому задаешь вопросы, значит ты еще больший дурак.

>Какие книги, посоветуй авторов? Я проебал ссылки

Что ты хочешь узнать?

>Какие книги, посоветуй авторов? Я проебал ссылки

Я выше упоминал nand2tetris. Хотя это не совсем книга, но так даже лучше зайдет. Это курс по построению процессора из отдельных вентилей 2И-НЕ, конечный итог - работающий на этом компьютере тетрис. Если бы ты задавал вопросы по этому курсу, то тебе наверняка бы кто-нибудь ответил. А так ты несешь бред и удивляешься не менее тупым ответам.

>Если ты не можешь объяснить ребенку на пальцах что то в течении минуты - значит ты это сам не понимаешь

Неправильная логика. Это бы означало, что все что ты "читал", писали люди, не осознающие того что пишут. А это явно не так.

>Про компилятор знаю, но принцип ты его понимаешь?

Понимаю, написал сам парочку простейших. Лежат рядом с кодом вышеприведенного процессора.

>Ну ты же сам понимаешь, что программа это не магия, а по сути управление логическими элементами и кодерами, которые из этих вентелей и состоят.

Машинные команды, из которых состоит компилятор, ничем не отличаются от машинных команд любой другой программы.

Похоже ты не осознаешь что такое процессор и что он делает. Причем не на уровне того что у него внутри, а что он выдает наружу. Если бы ты сам попробовал запрограммировать на ассемблере хоть что-нибудь, а потом вручную перевести код на ассемблере в машинные коды, то таких тупых вопросов точно бы не задавал. Но ты просто "читал", не напрягая мозги и не отвечая на контрольные вопросы. А потом ты наверное еще головой стукнулся, и в голове у тебя какие-то "кодеры" перемешались с компиляторами.

>но на уровне микро видимо мало кто понимает, кроме инженеров интела и т.п.

Специалистов по физике твердого тела тут действтительно не наблюдается. Но тут есть несколько анонов, способных придумать простенький процессор и нарисовать его схему на отдельных транзисторах. На это способны все плисоебы. Выше по треду тебе наглядное подтверждение.

>>26278

Именно такие в процессоре вряд ли окажутся. В вышеприведенном процессоре такого нет.

Или у тебя вопрос в том, как программа будет переводить десятичные числа (код 1 из 10) в двоичные (натуральный двоичный код)? Так это совсем просто, например посредством команд сравнения и условных переходов.

Все, мне надоело отвечать на твой тупняк. Если следующие вопросы будут не по курсу nand2tetris, то отвечать тебе не буду. Вопросы по этому курсу можешь задавать в этом треде.

>Какие книги, посоветуй авторов? Я проебал ссылки

Я выше упоминал nand2tetris. Хотя это не совсем книга, но так даже лучше зайдет. Это курс по построению процессора из отдельных вентилей 2И-НЕ, конечный итог - работающий на этом компьютере тетрис. Если бы ты задавал вопросы по этому курсу, то тебе наверняка бы кто-нибудь ответил. А так ты несешь бред и удивляешься не менее тупым ответам.

>Если ты не можешь объяснить ребенку на пальцах что то в течении минуты - значит ты это сам не понимаешь

Неправильная логика. Это бы означало, что все что ты "читал", писали люди, не осознающие того что пишут. А это явно не так.

>Про компилятор знаю, но принцип ты его понимаешь?

Понимаю, написал сам парочку простейших. Лежат рядом с кодом вышеприведенного процессора.

>Ну ты же сам понимаешь, что программа это не магия, а по сути управление логическими элементами и кодерами, которые из этих вентелей и состоят.

Машинные команды, из которых состоит компилятор, ничем не отличаются от машинных команд любой другой программы.

Похоже ты не осознаешь что такое процессор и что он делает. Причем не на уровне того что у него внутри, а что он выдает наружу. Если бы ты сам попробовал запрограммировать на ассемблере хоть что-нибудь, а потом вручную перевести код на ассемблере в машинные коды, то таких тупых вопросов точно бы не задавал. Но ты просто "читал", не напрягая мозги и не отвечая на контрольные вопросы. А потом ты наверное еще головой стукнулся, и в голове у тебя какие-то "кодеры" перемешались с компиляторами.

>но на уровне микро видимо мало кто понимает, кроме инженеров интела и т.п.

Специалистов по физике твердого тела тут действтительно не наблюдается. Но тут есть несколько анонов, способных придумать простенький процессор и нарисовать его схему на отдельных транзисторах. На это способны все плисоебы. Выше по треду тебе наглядное подтверждение.

>>26278

Именно такие в процессоре вряд ли окажутся. В вышеприведенном процессоре такого нет.

Или у тебя вопрос в том, как программа будет переводить десятичные числа (код 1 из 10) в двоичные (натуральный двоичный код)? Так это совсем просто, например посредством команд сравнения и условных переходов.

Все, мне надоело отвечать на твой тупняк. Если следующие вопросы будут не по курсу nand2tetris, то отвечать тебе не буду. Вопросы по этому курсу можешь задавать в этом треде.

> Хочу найти подробные схемы видеоконтроллера кр580вг75

Нахуя? Аналог делается без всяких схем собственно контроллера: http://www.danbigras.ru/RK86/Naladka/NoVG75.html

Вроде можно. На выход кондёр пожирнее, резистор на пару сотен Ом до земли.

Я слишком сноб, но меня так-то от элэмки корежит, а тут еще и плис питать от неё. Уф.

В моём случае там будет AMS1117.

61 Кб, 1246x967

61 Кб, 1246x967Форм-фактор. Понятно же, что он имел ввиду футпринт платы под шину на материнку.

This! Спасибо за перевод с битардского. Я просто ахуеваю сколько стоят отладки с интерфейсами PCI-E и SFP+

Они что блять из золота?

Может дешевле выйдет, если самому развести и заказать у китайцев?

С учетом вероятного проеба первой партии, и немногочисленности, будет раза в два дороже

Это не перевод, а попытка затраллеть (или нет, в случае только разъёма). Вообще это PCI Express Electromechanical Specification, не? Дешевле или нет, ящитаю, зависит от конкретной отладки или конкретно того, что тебе нужно, и в каком количестве.

возможно ли устроиться и зарабатывать нормальную деньгу (50-150) плисаном без диплома вообще? Или без диплома магистра?

Посмотреть тонущий тред никак? Я тебе даже ссылку на него оставлю https://2ch.hk/ra/res/127314.html (

>Или без диплома магистра?

С дипломом специалиста нормально. А с дипломом бакалавра сложно. Сразу же возникает вопрос почему не доучился. Обстоятельства или просто дурак?

> отладки с интерфейсами PCI-E и SFP+

> Они что блять из золота?

Они, прежде всего, предназначены для больших дяденек с серьёзным бизнесом, а не для гаражных ниггеров.

> Может дешевле выйдет, если самому развести и заказать у китайцев?

Ты точно уверен, что можешь уложиться в 200 долларов за готовое изделие?

https://www.aliexpress.com/store/product/Arria--PCIe-board/620372_32844162066.html

https://www.aliexpress.com/store/product/PCIe-development-board-Cyclone-IV/620372_32821486791.html

Как правило в руководстве компаний, которым в РФ нужны плисаны (оборонка) сидят дяди старой формации, воспитанные еще при Брежневе. А им ты хуй объяснишь, что бакалавр это высшее образование.

Высшее образование времён Брежнева безвозвратно ушло ещё в начале нулевых. А бакалавр это по сути научный работник, не заточенный под выполнение узко специализированных задач, но с развитым умом и большим количеством креатива. Магистр это уже по совковым меркам кандидат наук. Далее только доктор философии. Но как всегда у нас все смешалось и превратилось в кучу дерьма. Вся надежда на этот срок Путина, по словам будет восстановление разрушенной системы образования и подъем с колен собственной микроэлектроники.

>бакалавр это по сути научный работник, не заточенный под выполнение узко специализированных задач, но с развитым умом и большим количеством креатива

И хули тогда бакалавры делают в ВУЗах, которые готовят инженерные (читай, прикладные) кадры?

Он же написал, что у нас все как обычно перемешалось.

Однако не логично то, что даже первоначально бакалавр - это промежуточный этап перед магистром. Нет смысла готовить узкоспециализированного человека, чтобы потом еще пару лет готовить из него специалиста широкого профиля. Либо так не должно быть вообще, либо бакалавров должно быть два вида.

Жиза. Я начальнику отдела на собеседовании пять раз повторял, что диплом у меня уже есть. Бакалавра.

Я бы тоже с радостью нечто подобное практическое заимел.

А пока приходится задачки с работы делать.

Впрочем, кое-что могу подкинуть. Тут не книги, а брошюрки скорее. И да, они появились когда я петушил на VHDL.

Тут подробно описаны потоки типа FIFO.

https://www.springer.com/cda/content/document/cda_downloaddocument/9781461443001-c1.pdf

Тут сборник годных советов.

http://www.mrc.uidaho.edu/mrc/people/jff/vhdl_info/Ten_Commandments_VHDL.pdf

Но больше всего опыта в проектировании я получил, читая макросы на python от этих авторов.

https://github.com/enjoy-digital

https://github.com/m-labs

Куда лудше вкатываться в ПЛИС или стм32?

204 Кб, 300x400

204 Кб, 300x400В какую сторону вращается девушка?

Если по часовой стрелке - ПЛИС.

Если против часовой стрелки - STM32.

Очевидно стм32.

Стм-ку можно купить, сделать для неё плату из говна и палок однослойную, развести распаять и девайс готов.

ПЛИС для махараечных датчиков - оверкилл.

Если хочется - можно плисоебить чисто в редакторе с тестбенчем.

1013 Кб, 2560x1440

1013 Кб, 2560x1440Это называется внушение. Могу и аргументировать.

Желание перейти к ПЛИС - это желание анализировать. ПЛИС даст тебе знание внутреннего устройства контроллеров и процессоров. Желание анализировать возникает в левом полушарии мозга, и если оно активно - то девушка вращается по часовой стрелке.

Желание перейти к STM32 - это желание создавать. STM32 даст больше возможностей, власти для своих идей. Желание создавать рождается в правом полушарии и когда оно активно, девушка движется против часовой стрелки.

Лучше то, что тебе ближе.

>Надоело тупо подключать ардуино библиотеки для датчиков.

Учитывая это предложение, тебе лучше как следует изучить микроконтроллер в своей ардуине. Для начала ты можешь делать все то же самое на ардуиновской плате, но не использовать ардуиновское иде и библиотеки.

Ты наверное даже с регистрами в атмеге не разобрался? Представь себе, микроконтроллер, который стоит в ардуине, разрабатывался не для ардуины вовсе. Даже более того, существуют какие-то ардуины и на Cortex-M3. Если бы ардуины начали делать на STM32, а такая возможность есть, то что бы ты тогда делал?

>>27753

В целом верно, но однослойную плату под QFP-144 в домашних условиях вполне можно сделать. А CPLD в PLCC корпусах с панельками вообще можно на макетке паять.

Это печально, скоро совсем не получится потыкать осциллографом прямо в ноги FPGA. Хотя нет, серия 5576 никуда не денется.

Ну аналоговые сигналы можно и на другом конце потыкать, а не у ноги плисины. Конечно, есть всякая срань шумовая по пути, но я уж не знаю, насколько это важно.

Так то аналоговые сигналы обычно непосредственно в ПЛИС не заходят. Входной аналоговый сигнал смотришь на одном конце, выходной на другом, а синхронизируешься от вывода ПЛИС, например.

Ну и потом, во FLEX10K ничего такого не имеется.

2,1 Мб, 2560x1440

2,1 Мб, 2560x1440Мне кажется для подобных целей достаточно сделать отладочные пятаки на этапе проектирования печатной платы.

Плюс, насколько я знаю, пятаки, к которым паяется BGA обычно делают сквозными и их можно потыкать с другой стороны печатки? Разве нет? Сам редко этим занимаюсь.

60 Кб, 1202x1002

60 Кб, 1202x1002Антон, скажи что у меня глюки.

Неужели реализация обычного юарта занимает 342 триггера и в самую младшую FPGA влезет всего 1.5 юарта ?

76 Кб, 850x1169

76 Кб, 850x1169> a16450

> обычного юарта

А ты думал — в сказку попал? https://www.altera.com.cn/content/dam/altera-www/global/zh_CN/pdfs/literature/ds/ds16450.pdf

Ну не триггеров, а логических элементов.

Плюс, это же приемо-передатчик. Еще и перевод из последовательного в параллельный, та еще морока.

Поддвачну. В планах накатить 8086 или что-нибудь слабее например 6205, поэтому советуйте платку с оперативкой сразу.

На всякий случай скажу очевиднейший факт, который, возможно, тут не все знают. В отличие от микроконтроллеров, тут для чего-то более-менее сложного без симуляции не обойтись. Непосредственно для обучения плата не требуется. Поэтому если что-то и покупать, то в основном для того чтобы просто посмотреть как оно работает.

Книгу там выше по треду советуют >>27693 Сам я советовать не буду, т.к. то что я читал, мне не понравилось.

>>28926

>6205

Может 6502?

>с оперативкой сразу.

В самих FPGA достаточно много блочной двухпортовой памяти. В весьма небольшой EP4CE10 этой памяти 414 кбит, в EP4CE22 594 кбит, по моему этого вполне хватит для игрушки на 6502. Если все-таки хочется отдельную память, то стоит определиться с ее типом.

А схема где? Или ты китайцам для ее получения писал?

Уж лучше взять https://store.digilentinc.com/arty-s7-spartan-7-fpga-board-for-makers-and-hobbyists/ хотя в сумме с доставкой выйдет дороже. Но для задач того анона возможно лучше взять со статической памятью.

> хочу вкатиться в FPGA

> какую плату купить для начала?

Если говорить про альтеры (с хилыми не работал, так что посоветовать не могу), то почти любую на младших камнях из семейства «Циклон 4» (EP4CE6/EP4CE10) и приемлемым количеством мигалок и переделок (чтобы не ебаться с макетками и проводами), плюс программатор (китайский клон USB blaster):

https://www.aliexpress.com/item/ALTERA-Cyclone-IV-EP4CE6-FPGA-Development-Kit-Altera-EP4CE-NIOSII-FPGA-Board-and-USB-Blaster-downloader/32792622551.html

https://www.aliexpress.com/item/Free-shipping-Altera-CycloneIV-FPGA-Development-board-EP4CE6E22C8N/32715249531.html

https://www.aliexpress.com/store/product/Free-shipping-altera-EP4CE6F17C8N-board-fpga-board-altera-board-altera-fpga-development-board-fpga-development-board/620372_32795496067.html

https://www.aliexpress.com/store/product/only-E10-SDRAM-altera-EP4CE10F17C8N-board-fpga-board-altera-board-altera-fpga-development-board-fpga-development/620372_32800480331.html

>>28926

Тоже самое. Додревнюю восьмибитную ЭВМ можно успешно впихнуть в EP4CE10: http://www.electronicsfun.net/RU/archives/932

>>29062

Ну, в моём случае китаец дал ссылку на файлообменник, с архивами (схемы, примеры и немного документации в стиле «шоаррская лиса»).

P.S. Плисаны, я тут охуительную хуйню нашёл. «Пердуина» с MAX10 вместо микроконтроллера: https://www.aliexpress.com/store/product/Mini-Altera-MAX10-10M02SCM-10M8SCM-10M08SAM-FPGA-Development-core-Board-compatible-with-Arduino-Raspberry-Pi/829772_32881985871.html

Прикол они мои клиенты, члены деревянные им отгружаем

Помню, рекомендовали сиську читать, но там разве не применительно к их аппаратуре?

Читал стандарт IEEE на 802.3 - маловато\сложновато. Маки, хуяки. Ничего не ясно.

Схему китайцы скинули, ага. За ссылку спасибо, кое-что присмотрел там интересное.

> Плюс, насколько я знаю, пятаки, к которым паяется BGA обычно делают сквозными

Ничего ты не знаешь, Джон Сноу. Потыкать можно в переходные отверстия, через которые ноги соединяются с другими элементами схемы. Сами контактные площадки не сквозные, а поверхностные.

Ты странный. Хочешь вкатываться на низком уровне, а стандарты тебе СЛОЖНА. Кроме того, низкий уровень - это что? Схемотехника PHY? Логика MAC? Алгоритмы протоколов верхнего уровня? Будешь делать свой W5300 на ПЛИС? Будешь делать свой TCP/IP-стек на STM32?

Хм... А может 8 бит процессор с программно настраиваевым декодером команд и его возможности в эмуляции на нём всяких микроконтроллеров?

Типа перспективы развития реализации аппаратного эмулятора...

Хз чушь несу

Она идёт вперёдъ

Ой ля, спс а то я сам всё это учил а как называется хз

Бледь.. А если я плисоёб и у меня девушка тоже вращается против часовой стрелки?

Я получается лентяй без желания создавать?

Молодой человек, эта девушка не для вас вращается!

Да! Девушке явно не хватает мнимой компоненты

Ну вот поморгал ты светодиодиком.

Потом двумя.

Потом сделал рс232 приемник, ...

как там дальше?

И как плохого плисоеба отличить от хорошего? Быстро кодит? Мало блоков использует?

>как там дальше?

VGA, общение с памятью, SPI, I2C, USB, 10/100 Ethernet PHY, гигабитные приемопередатчики, общение с АЦП/ЦАП, интерфейс JESD204B, шина AXI, встроенные процессорные ядра (Microblaze/Nios), ARM.

Отдельно - ЦОС, фильтры, приемники, демодуляторы, SDR, обработка звука/видео/изображений, нейросети.

Еще отдельно - криптография, майнинг.

> USB, 10/100 Ethernet PHY, гигабитные приемопередатчики

Это зависит от наличия бабла на дорогие ПЛИСы и корки, или погромиста (не быдлокодера) под боком.

> Ethernet PHY

У тебя три ошибки в слове MAC

>дорогие ПЛИСы и корки, или погромиста (не быдлокодера) под боком

Необязательно, я 100 Ethernet в одно рыло поднял, и без всяких NIOS-ов и прочих говнософтовых и хардовых процов. А все нужные корки есть в свободном доступе.

>шина AXI, встроенные процессорные ядра (Microblaze/Nios), ARM.

Ну это так-то уже куски С кода в процессорной среде по большей части, не?

>Это зависит от наличия бабла на дорогие ПЛИСы и корки, или погромиста (не быдлокодера) под боком.

Зависит. Но вопрос был какая линия прогресса у плисоеба. А в серьезных конторах хотят, чтобы плисоеб мог смахараить свич на ПЛИС.

>Ну это так-то уже куски С кода в процессорной среде по большей части, не?

И? Ты думаешь, плисоеб не должен уметь кодить на C?

> идеологически верно и политически грамотно

делать ему длительность один период тактовой частоты и подавать его на вход EN

>EN

Никак не могу понять, этот EN - обычный вход разрешения, завязанный на вход D, или же какой-то спец. вход завязанный на тактовый вход?

мимо

И какие вещи надо купить и где.

Какие книги почитать.

Но главное это основные вехи Мастера, так сказать план.

> вход завязанный на тактовый вход

This. Твой строб будет тактирован основной тактовой частотой.

Этого двачую! Логический анализатор для начинающего плисоёба - отличный проект. Можно ещё 8-битную игровую приставку из ничего (от вентилей до написания игрули) попробовать замутить.

В том, чтобы найти нужные куски кода, собрать проект, запустить и чтобы работало как надо.

>count enable

Это в счётчиках. Это синхронный вход, подаётся через комбинационные схемы на D-вход.

Мне интересен именно clock enable у D-триггера. Желательно схему такого триггера увидеть.

Насколько я понимаю, это можно сделать не одним способом, но например в структурных схемах МК рисуют вентиль И. А в логической ячейке ПЛИС уже есть аппаратный триггер, и как там у него внутри сделан вход clock enable, производитель не расписывает (ну, по крайней мере, Альтера для Циклона не расписывает).

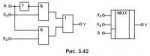

>1 пик

Если сделано как на (b), то это хуета, лучше сразу делать как на (а).

Вкинь, плиз, страницу с рисунком 3.18.

digital-design-and-computer-architecture-russian-translation.pdf

160 Кб, 688x987

160 Кб, 688x987Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. — 3-е изд. 2010

По такой схеме повышаются требования к сигналу EN, он должен быть таким чтобы на тактовом входе не образовались пички.

И вообще, комбинационные схемы и другие на тактовых входах крайне нежелательны - синхронное проектирование же.

Вот тут подробнее рассказывается

https://youtu.be/82MIcxi5pPo

https://youtu.be/JpUUdEEKZeg

Бочку делаешь?

Сколько процентов рабочего времени ты занимаешься именно разработкой - проектированием структурных схем, кодингом, симуляцией, пердолингом с железкой?

61 Кб, 794x593

61 Кб, 794x593STM32F103ZXXX как основной узел ..., нутыпонел.

XC6SLX9-2TQG144C как вспомогательный.

На плате будут распаяны: слот под microSD, SDRAM, SPI flash (S6 заведётся от W25QV?).

Чего ещё не хватает для универсализации? кроме мозгов

Да.

Почему бы не грузить S6 "основным узлом" в режиме slave serial? А так в списке поддерживаемых spi flash этот winbond вроде бы есть.

Хочется, чтоб он и в автономном режиме работал.

Разве у Z нет FSMC? Я, собс-но, из-за него и выбрал. В каталоге он не отмечен, но в описании есть, в кубе тоже.

https://www.st.com/en/microcontrollers/stm32f103zg.html

А в даташите пишут что есть, более того, пишут, что у V серии FSMC наоборот кастрирован в отличии от Z. Это ты наверное в таблице на сайте посмотрел, так её наверняка какая-нибудь секретутка из офиса заполняла, верить ей не стоит, в отличии от даташита.

Ан нет, здесь попал.

>The FSMC is embedded in the STM32F103xC, STM32F103xD and STM32F103xE performance line family.

Но при этом в другом даташите:

>The FSMC is embedded in the STM32F103xF and STM32F103xG performance line family.

Получается, все с буковками должны иметь FSMC, но в F103R в кубе нету нихуя, хотя в описании есть. Это куб мозги ебёт или документация?

Расширенный CS есть только у Z, да.

Орнул с даташита, раздел Pinouts and pin descriptions. У LQFP64 нет выводов к FSMC. Это выглядит как "вам полагается FSMC, но мы вам его не дадим потому, что у вас ножек нету".

>вам полагается FSMC, но мы вам его не дадим потому, что у вас ножек нету".

И хуле орать? Бери чип с нужным количеством ног и радуйся. Или ты предлагаешь писать отдельный даташит под каждый корпус?

Не, ну там на 11-ой странице в Table 2 и так написано что-то, но можно же эту таблицу было вывалить сразу в описании на сайт или, хотя бы, добавлять исключения в описание. А то получается, что в описании всё есть, а дальше мелким шрифтом на n-ой странице написано, что у одного нихуя нет, а другой кастрирован. Это как если при покупке смартфона в описании нормальные характеристики, а в инструкции меленько будет написано, что телефона нет, собс-но, 128Гб в другой модели, и вообще это тетрис.

Ты будто первый раз попал на сайт st. Сейчас еще более-менее упорядочили, а еще пару лет назад там был пиздец, гроб, кладбище.

Как будто это что-то оправдывает. Получается, что и сейчас можно в говно наступить.

Есть sigA STD_LOGIC_VECTOR, скажем, на 32 бита,

и sigB STD_LOGIC.

Как красиво назначить некоторые биты вектора равными значению сигнала?

Т.е., чтобы sigA(13 downto 7) <= sigB. Напрямую, естессно, не работает. Каждый бит прописывать - тупо.

Я помню была какая-то ебатория с фигурными скобками типа <={N, (sigB)} или типа того. А может то в верилоге было.

Вспомнил сейчас про loop, но не люблю его использовать. Хз как он синтезируется и что там по таймингам.

Потому что это бесполезный высер про смену языка.

На уровне смены железки.

Смены места работы.

Смены спецухи.

Смены места жительства.

Поставил вам анон задачу решать: есть суп вилкой. Нет, давайте не будем её решать, давайте советовать ложку.

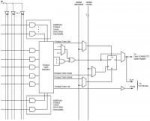

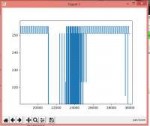

65 Кб, 944x900

65 Кб, 944x900Попробовал реализовать АРУ. Вот что вышло:

https://www.youtube.com/watch?v=c6bMfBvcjDE

Описание на Верилоге - на пикче. На входе - сигнал в спектре шириной 3 кГц после КИХ-фильтра.

Из-за мгновенного действия детектора усиление сильно проваливается от грозовых разрядов, и из-за ступенчатой регулировки слышно щелчки, пока работает какая-нибудь станция.

Как можно попроще сделать регулировку плавной? Как текущий вариант допилить? Может фильтр простенький какой (скользящее среднее, например), чтоб щелчки сглаживать?

14 Кб, 550x153

14 Кб, 550x153Почему бы тебе не сделать схему с обратной связью? Так же как в аналоговых приемниках делают.

Детектор - просто взятие модуля. Интегратор сигнала ошибки - ФНЧ и вычитание из порога. А управляемый усилитель - умножитель.

Ебани мне РЛС.

Ну вот зачем ты делаешь мне боль? Зачем ты делаешь кровь мои глаза?

http://verilog.renerta.com/source/vrg00004.htm

Попробую.

Тут встаёт вопрос выбора разрядности.

Допустим, в качестве фильтра беру скользящее среднее длиной 2048 семплов (больше по степеням двойки в такт не влезает).

Имея на входе 17 бит, при длине 2048 и худшем случае, когда на входе - максимальное постоянное напряжение, получаю увеличение разрядности на 11 бит. Итого, на выходе фильтра имеем разрядность 17 + 11 = 28 бит.

Тут первая непонятка:

Какая разрядность вычитателя должна быть?

Предлагаешь использовать case или есть более интересные предложения?

> Боги рассыпухи смотря

т

Очень мееееееееееееееедленно, потому что могут онли в сотни килогерц максимум.

"Ленинград"

Сейчас у спектрумистов на барахолке полно новодешьных печатных плат для спектрумов и не только.

29 Кб, 736x526

29 Кб, 736x526>>32876

Всё, разобрался. Спасибо за подсказку. Настолько всё просто получилось, что удивляюсь, что сам не допер и нагуглить не смог, пиздец.

https://www.youtube.com/watch?v=kVJAphWwxNc

Про дискретность регулировки усиления на 2:28 возможно хуйню сказал, ну да похуй.

Вот стоит перед нами задача. Из входов с помощью магии получить выходы. Пишем вот на HDL всякое и первоначальными критериями того, что всё удалось является адекватная временная диаграмма, количество занимаемых ячеек и работа непосредственно на железке.

А вот как писать код чтобы: было низкое энергопотребление или высокая скорость выполнения или минимальное количество ячеек?

На что ориентироваться, как это на коде отражается?

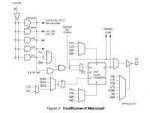

63 Кб, 821x707

63 Кб, 821x707Вот в циклоне, как показано на схеме, предусмотрено переключение направления на ходу, а не только при конфигурации. В других ПЛИС аналогично. В чем проблема то?

>низкое энергопотребление

Меньше переключений, в том числе и отключение тактовой на неиспользуемых в данный момент частях схемы.

>высокая скорость выполнения

Чаще разбивать толстые комбинационные схемы триггерами.

>минимальное количество ячеек

Тут только оптимизация на ранних уровнях проектирования.

HDL-код - это всего лишь способ создания схем. Можно схемы в графическом редакторе рисовать, можно напрямую в ChipPlaner-е структуру задавать, от этого ничего не меняется, просто в HDL-е это всё делается быстрее и удобнее. А чтобы нормально кодить, надо более менее представлять как желаемая схема должна выглядеть в графическом виде.

Можешь видосики глянуть, может что-то интересное найдёшь

https://www.youtube.com/playlist?list=PL4UMfOeGYsvZs-gvs0dC8oO3HXrmGC1bm

>Хотя как это ретранслируется в код пока неясно.

FPGA основана на таблицах истинности+специализированные блоки (память, умножители). Смотри даташит конкретной плисы. Например LE четвертого циклона - это любая логическая функция, описываемая 4 входами и одним выходом + один бит памяти + логика роутинга и синхронизации.

Соответсвенно прикидывай, через сколько логических функций 4bit to 1bit выражается твоя логика.

Ну вот что, например, лучше:

case (a) is

when 0 => ..

..

when 99 => ..

(т.е. мультиплексор на 100 входов)

или

if a = 1 then ..

elsif ...

(т.е. 100 триггеров(?)).

Триггер сам по себе реализуется всегда тяжелей, но в логике плиса - хз, там же и правда, лут, алу, вся хуйня.

>Триггер сам по себе реализуется всегда тяжелей

В ПЛИСе триггер не реализуется, они там уже есть, точно так же как и ПЗУ на которых реализуются комбсхемы.

Минимизировать схему, по большому счёту, нужно на ранних этапах проектирования, т.е. перед тем как начать кодить думаешь: "а нужен этот модуль/часть схемы, или без него можно обойтись", более тщательно прорабатываешь архитектуру. А если по мелочи то, в качестве примера, можно привести счётчик с параллельным переносом и сквозным.

93 Кб, 1080x795

93 Кб, 1080x795>но в логике плиса - хз

В самом деле хз...

Ты бы хоть что-нибудь почитал, прежде чем за ПЛИС браться.

Везде пишут просто

ram_data_out <= memory(to_integer(ram_addr));

Понятно, что для более-менее больших объёмов делать

case (to_integer(ram_addr)) is

when 0 => ram_data_out <= memory(0);

...

(т.е. мультиплексор) заебешься. Разбивать его на несколько маленьких? Или есть еще какая элегантная реализация, типа сдвигового регистра и пр. ?

>Везде пишут просто

>ram_data_out <= memory(to_integer(ram_addr));

Так и чем тебя это не устраивает?

Эта строка в любом компиляторе и на любой железке будет одинаково реализовываться?

Если железка поддерживает реализацию массивов данных, то да.

Как сделать обмен комп<->плис? Первое что пришло в голову - UART, но блин медленно, передавать/принимать желательно за раз 64 байта, по возможности быстро, хотя бы 8 байт за такт. Какие ещё варианты? Параллельный стык колхозить типа LPT?

>не знаю как прошеца в очередной раз контроллер 51 архитектуры

>контроллер 51 архитектуры

>тред про ПЛИС

Шел бы ты нахуй отсюда, петушок.

Это массив данных на аппаратном... в общем размер переменной для вычислений, пока все 64 байта не придут, вычисления не начинаются.

Даже если скорость поднять, то все равно медленно? Большинство USB-UART переходников работают до 460800 бод без проблем, а некоторые на порядок больше тянут.

Из простого можешь еще использовать FT245, FT232 и подобные.

>Data transfer rate to 1 Megabyte / second - D2XX Direct Drivers.

>Simple interface to MCU / PLD / FPGA logic with simple 4-wire handshake interface.

>>33646

Ну можешь просто байты считать. Либо можно начинать (и/или заканчивать) посылку с уникальной последовательности, если боишься обрывов связи.

>пока все 64 байта не придут, вычисления не начинаются

Для этих целей ставится буфер, который выдает сигнал валидности. Выдает только тогда, когда в него набъется нужное количество данных.

Перестань ебаться в глаза и еще раз прочитай что я писал. Тебе подойдет FT232.

Ты че там, бетховенов майнишь что ли?

Ну это если есть свободный слот, то да, топ.

Собери аппаратный дешифратор данных, у чекистов что-то подобное сейчас в ходу.

84 Кб, 385x280

84 Кб, 385x2802. Есть ли разница в описании комбинационной логики между:

a)

process(A1,A2)

begin

result <= A1 and A2;

end process;

B <= result;

б)

B <= A1 and A2;

3) Есть ли разница в описании:

а)

if (A1 = '1')

then if (A2 = '0')

then

б)

if (A1 = '1') and (A2 = '0')

then

1. Систем верилог - расширение верилога с блекджеком и свистоперделками.

2, 3. С такими вопросами можешь нахуй идти.

171 Кб, 462x380

171 Кб, 462x380>Всё, разобрался. Спасибо за подсказку. Настолько всё просто получилось, что удивляюсь, что сам не допер и нагуглить не смог, пиздец.

Я, конечно, привык к человеческому долбоебизму, но всё равно иногда охуеваю.

Вот здесь я тебе советовал сделать так, как ты сделал сейчас:

https://m2ch.hk/ra/res/138868.html#278025

Вот здесь я объяснял, что будет происходить от импульсных помех:

https://m2ch.hk/ra/res/138868.html#278445

Вот здесь я тебе предсказывал, что ты соснёшь со своим бараньим упорством не слушать хороших советов:

https://m2ch.hk/ra/res/138868.html#278470

Поздравляю, ты всё-таки пришёл к И-регулятору, всего-то за один год и четыре месяца. Ещё и пожаловавшись, что оно не нагуглилось. Просто пиздец, какие же люди долбоёбы, вообще пиздец.

149 Кб, 1899x742

149 Кб, 1899x742Только In System Sources and Probes Editor для попытки снятия топологии неизвестной платы. Заебатый квест. Большая часть выводов (может 500 из 740) распознана таким методом, исключая выводы высокоскоростных трансиверов.

Пока разбирался с SignalTap-ом столько косяков нашёл и расхождений с документацией. Вот думаю, то ли я и дурак и не понимаю, то ли действительно индусы пишут.

Они ещё и официальные видеоруководства записывают. От их акцента полное чувство индусизма происходящего.

84 Кб, 640x640

84 Кб, 640x640"хай маль диль флендс. тюдель аль виль тёльк абальт илитлёниксь"

https://www.reddit.com/r/MonsterHunter/comments/983851/25_of_cpu_usage_in_monster_hunter_world_is_for/

Щито поделать. Индусы пилят видосы.

Жри чё дают, мразь.

2. Есть ли годные ресурсы по всему этому кодингу на русском языке (ну кроме мемных ссылок на марсоход и тот плейлист на тытрубе про цифровую схемоту) или дефолтный гуглеж на английском всё еще единственный годный вариант?

Обгоню всех на повороте и скажу, что слышал про IEEE std.

Не найду полином для расчета. Вообще можно ли считать это через полином? Или только через сумматор?

Тогда только суммировать... полиномами только общий CRC Ethernet фрейма считаеться

Если не буду считать КС, моя железка будет поддерживать протокол лишь условно. Для ардуиноподелок такой подход конечно подходит, но для коммерческого продукта врядли.

Не то что переборщили а сотворили лютую хуету. Вот что бывает, когда низкоуровневые протоколы пишут высокоуровневые программисты.

Как по мне, если хочешь сократить латенси. например, это можно не считать. Ибо у тебя пейлоад тоже в чексуме

Как я жалею в такие моменты, что плохо знаю математику. Сейчас бы вывел какую-нибудь функцию подсчета КС.

В голову не приходит ничего лучше, кроме как построить конвейер.

А как не через конвеер? Шморгать память?

Ну, еще придумал способ упростить. Вбей в заголовок не нулевую константу, а в пейлоад в конец вставь КС, если протокол пзволяет добавить 2 лишних байта

>Вбей в заголовок не нулевую константу

И рандомный маршрутизатор/стек ОС в цепочке тебя нахуй с ней пошлет

>Схуяли, это стандарт

Стандарт - это нули, всё что не нули - значит контрольная сумма оппа-а пакет-то битый, нахуй его.

>В голову не приходит ничего лучше, кроме как построить конвейер.

А так у тебя конвейеров нету? А как данные передаются тогда? Только не говори, что процессором без DMA.

не, ты просто не понял. Тебе не важно чем подгонять контрольную сумму к правильному значению, можно полем, а можно данными. Позиция по сути не важна

Если интерфейс согласован до пина, а на кристалле показывает говно - это фейл?

А если наборот?

Заебали эти DDR4 с их ODT.

Чем показывает? На каком кристалле, плисины, памяти? Может, не написал констрейны для i/o standard и line termination. А может, и фейл, да.

Это на стадии моделирования разводки.

Модели выводов прописаны соответственно в IBIS файлах.

Показывает, например, на чтении у ноги FPGA хуйню, а на кристалле - норм. (odt на ноге плиса включен)

Ну вклинься между акси мастером и слейвом, и считай в процессе передачи, не должно быть слишком сложно.

1) Нахуя на циклоне нужны VREF для банков пинов?

2) Что дает выбор стандарта напряжений логических уровней в пин планере квартуса?

>Нахуя на циклоне нужны VREF для банков пинов?

https://en.wikipedia.org/wiki/Stub_Series_Terminated_Logic

> Что дает выбор стандарта напряжений логических уровней в пин планере квартуса?

Требуемую совместимость с другими потрохами на плате (оператива-хуератива, цапы-хуяпы, шины-хуины)

>Требуемую совместимость с другими потрохами на плате (оператива-хуератива, цапы-хуяпы, шины-хуины)

Не понял, поясни плиз.

12 Кб, 256x197

12 Кб, 256x197Спасибо. Держи няшку.

Короче все оказалось проще. Заголовок MAC-уровня передается за 14 тактов. На предыдущей стадии конвейера просчитываю предварительную КС UDP-payload. Окончательную КС считаю за 5 тактов во время передачи MAC. Можно было не ломать голову.

Однако, задача с ускорением подсчета КС интересная, так и не придумал рещение.

Шпиён! За меня ответил.

>2) Что дает выбор стандарта напряжений логических уровней в пин планере квартуса?

Разные стандарты определяют допустимые диапазоны напряжений и токов на выводе, надо читать на эту тему мануал плисины и даташит железки, к которой коннектится плис. (Те же jedec для DDR, например).

>джава для петухов.

вот сейчас обидно было

>мне похуй на зарплату

ой ой ой передумаешь

мимо проходил

Доброта.

Я был и остаюсь в таком состоянии диагноз есть, что про ЦОС-тред вообще забыл, да и не мог нихуя делать, не соображал почти.

Для любителей садо-мазо можно предложить 74HC299 - есть и параллельная загрузка и последовательный ввод-вывод.

С тебя логика как переключать режимы загрузка-вывод (может и обойдется даже без инвертора на S1) и как отличать актуальные данные или нет.

За лучами поноса в >>16943 (OP)

И не надо мне писать что нужно знать английский. Мне понятно что все равно в итоге придется читать на английском, но хотя бы основы я хочу прочитать на русском.

По-русски это, видимо, звучит как "написание тестбенчей".

Отвечаю сам себе, нашел одну книгу.

>Проектирование и верификация цифровых систем на кристаллах. Verilog & System Verilog

>Хаханов В.И., Хаханова И.В., Литвинова Е.И., Гузь О.А.

Книга выглядит как-то не очень, слишком похоже на перевод. Скорее всего это перевод и есть, только надерганный из разных источников.

В книге рассказывается об использовании assert-ов и псевдослучайном тестировании. Хотелось бы еще почитать про UVM, OVM и прочее.

Так если через SPI конфигурируется, то разве нельзя микроконтроллером через SPI сконфигурировать?

мимо

>Так если через SPI конфигурируется, то разве нельзя микроконтроллером через SPI сконфигурировать?

Там хитрожопая анальная дрм-защита на проверку "а специальные ли флешки за 100$ ты используешь?".

Раскуривай ->

https://www.xilinx.com/support/documentation/user_guides/ug380.pdf

С Xilinx не работал, у Altera - да, есть проверка типа памяти только при заливке конфигурации в ПЗУ, но не при чтении конфигурации после подачи питания.

хотя наоборот тоже интересно

SERDES из мира Ethernet вряд ли подойдет - используется перекодирование 8 бит (исходные данные) в 10 бит (в линии).

Может помогут всякие LVDS драйверы для Flat panel типа DS90CF383? Чуть больше 24 бит заталкивает в 5 LVDS линков.

Чуваку постом выше твоего будет полезнее раскурить.

Жесткий челикс.

Хуйню не неси, анальный страдалец. Протокол открыт и документирован.

Накидайте пожалуйста мануалов для быстрого старта помигать светодиодами, в интернете ч нашел одну хрень

С бордой идут примеры

314 Кб, 1500x1000

314 Кб, 1500x1000Камень - это как на этой фотографии? Ну это больше по спортивной тематике.

Перед тем как что-то покупать, тебе нужно было читать что-нибудь по основам цифровых устройств, например Угрюмова.

https://twitter.com/ico_TC/status/823883792754634752

Когда-то спрашивал, еще раз спрошу.

Есть слитая конфигурация с мелкой CPLD от Lattice. Как/чем превратить конфигурацию во внутреннюю схему межсоединений CPLD чтобы попытаться понять что там реализовано внутри?

Интересно, существуют ли кадры, задающие вопрос на пост с ответом?

Смотря что ты называешь практической пользой.

Но зачем тебе для этого ПЛИС?

Простой счетчик на ПЛИС даже не будет работать на такой частоте. Разве что только приспособить serdes. Но на такую частоту serdes в циклонах и спартанах вроде бы не дотягивает, придется все равно ставить внешний предделитель. Более того, serdes вообще зачастую отсутствует в дешевых сериях. Для записи на флешку придется использовать nios/microblaze (особенно если ты хочешь использовать файловую систему) или снаружи приделывать микроконтроллер, при этом сам сами счетчики будут занимать мизер относительно nios/microblaze.

Поэтому нет никаких причин делать такое на ПЛИС. Тому анону вроде как нужно было очень много каналов, а частоты были относительно низкими, поэтому ему был смысл использовать ПЛИС.

ну мне 8 каналов надо, забыл написать :)

ну есть вариант цайпрес 5 поставить, кто нибудь с ним работал? как он?

Спасибо, за разъяснения, посоветуй годные счётчики, прескалер, и коммутатор для этих целей.

>годные счётчики, прескалер

Не знаю, не делал такого. В качестве предделителя можно взять микросхему синтезатора частоты. Пользуйся параметрическим поиском на диджикее.

Я так и не понял что ты в итоге хочешь получить. Если тебя устраивает одна секунда длительности измерения и ты собираешься использовать в качестве опорного генератора обычный кварцевый не термокомпенсированный, то можно поставить предделитель на 1000. Тогда в точности почти ничего не потеряешь даже на твоей нижней границе частоты и снизишь максимальную частоту до 10 МГц. Разные варианты есть, в зависимости от желаемого результата.

Другой вариант это сделать одноканальный частотомер и на вход поставить демультиплексор.

Предделитель думал на счёт upb1505 , длительность измерения 10сек, опора 10Мгц термостптированныйтермостптированный , либо стандарт частоты.

Да, я тоже подкмпл, что канал один, а раз в На вход коммутатор и переключать раз в 10 сек

Можно выбрать что угодно, но в пределах разумного

А какие предложения?

130 Кб, 905x1280

130 Кб, 905x1280Поясните за task и function. Для чего нужны? В каких случаях их применение оправданно? В чём их преимущество перед обыкновенными модулями?

Функции и таски можно сравнить с макросами в Си. В функции можно запихивать только комбинационную логику. В таски можно уже вставлять последовательностную логику.

По сравнению с модулями, функции можно пихать практически куда угодно - в assign, initial, объявления. Например, пользуясь функцией логарифма удобно делать модули с параметризуемой разрядностью. Таски в принципе можно использовать для синтеза, но я их использую только для симуляции, т.к. часто сложно представить во что синтезируется код с ними.

Если модули можно образно представить как готовую печатную плату с детальками, то таски - нельзя. Например, вставили в таск ожидание фронта сигнала а потом вызвали несколько таких тасков друг за другом, во что оно синтезируется (если сможет конечно)? Это явно не всегда можно представить в виде последовательного соединения модулей.

Похую, назначаем вместо SubLVDS/LVDS приёмники DIFF_HSTL_I_18, назначаем вместо дифференциального single-ended терминаторы потому что DIFF_TERM есть только на LVDS эквивалент 50 Ом на 0.9В с p-сигнала и n-сигнала. То, что надо, казалось бы? Но вот хуй, данные принимаются неправильно.

Для сравнения берём отладку KCU105, она умеет в DIFF_HSTL_I_18 и в SubLVDS. Проверяем SubLVDS с DIFF_TERM — работает. Проверяем DIFF_HSTL_18_I, терминация — single-ended эквивалент 48 Ом на 0.9В для p-сигнала и для n-сигнала — тоже, сука, работает.

Почему так? Почему данные сенсора принимаются на Kintex Ultrascale KCU105 по стандарту DIFF_HSTL_18_I без проблем, а на Kintex 7 KC705 по тому же самому стандарту DIFF_HSTL_18_I — криво и косо? Что я не учёл?

>эквивалент 50 Ом на 0.9В

>эквивалент 48 Ом на 0.9В для

Например.

Пины дифференциальные, надеюсь, к одной паре заводил?

А то у меня был косяк, когда дифф. пару соединил с N и P, но только N была с 12L, а P с 13L.

Ну и может второй класс hstl пойдет?

>По сравнению с модулями, функции можно пихать практически куда угодно - в assign, initial, объявления.

Ну так почему нельзя создать модуль нужной комбинационной схемы и вставить его себе в код, ведь не обязательно комбсхемы подключать через assign?

Есть ли такой случай когда функцию нельзя заменить на модуль?

Если я правильно понял функции и задачи удобны по большей части в моделировании, в синтезе и без них вполне можно обойтись.

>Ну так почему нельзя создать модуль нужной комбинационной схемы и вставить его себе в код, ведь не обязательно комбсхемы подключать через assign?

Синтаксический сахарок. Для модуля надо писать объявление самого модуля, цепей, подключать цепи к портам, причём отдельно от описания прочей логики. Функцию где понадобилось, там и вставил.

>Есть ли такой случай когда функцию нельзя заменить на модуль?

Например, ты пишешь модуль с параметризуемой шириной шины, в параметре указываешь максимальное значение на шине, а ширину шины вычисляешь при помощи функции, чтобы это значение туда влезало.

>Ну так почему нельзя создать модуль нужной комбинационной схемы и вставить его себе в код, ведь не обязательно комбсхемы подключать через assign?

Это ты про что? При чем тут assign? Запись с функцией обычно будет короче.

>Есть ли такой случай когда функцию нельзя заменить на модуль?

С функциями можно проводить вычисления при инициализации и объявлении. Вычислять и задавать требуемую разрядность, хотя бы. Вот тебе вполне синтезируемый пример использования функции $clog2 https://github.com/minad/vle/blob/master/shifter.v

>Если я правильно понял функции и задачи удобны по большей части в моделировании, в синтезе и без них вполне можно обойтись.

Скорее только таски (по моему мнению). Функции для синтеза наоборот вполне удобны.

Вот еще тебе пример использования функции для инициализации памяти >>26151 В более сложных случаях это может быть не чтение из файла, а вычисление на ходу.